Texas Instruments MEMORY **GENERAL DESCRIPTION**

.

### MANUAL REVISION HISTORY

Explorer™Memory General Description (2533592-0001)

Original Issue .....August 1985

© 1985, Texas Instruments Incorporated. All Rights Reserved.

No part of this publication may be reproduced, stored in a retrieval system, or transmitted, in any form or by any means, electronic, mechanical, photocopying, recording, or otherwise, without the prior written permission of Texas Instruments Incorporated.

The computers, as well as the programs that Tl has created to use with them, are tools that can help people better manage the information used in their business; but tools—including Tl computers—cannot replace sound judgment nor make the manager's business decisions.

Consequently, TI cannot warrant that its systems are suitable for any specific customer application. The manager must rely on judgment of what is best for his or her business.

Printed in U.S.A.

iv Manual Revision History

### THE EXPLORER<sup>™</sup> SYSTEM HARDWARE MANUALS

| System Level<br>Hardware<br>Publications        | Explorer Unpacking and Inventory                                                                                                                                                                                                                                                                                                                |

|-------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| System Enclosure<br>Hardware<br>Publications    | Explorer 7-Slot System Enclosure General Description.2243143-0001Explorer 2-Megabyte Memory General Description.2243147-0001Explorer Memory General Description.2533592-0001Explorer Processor General Description.2243144-0001Explorer Display Unit General Description.2243151-0001Explorer System Interface General Description.2243145-0001 |

| Mass Storage<br>Hardware<br>Publications        | Explorer Mass Storage Enclosure General Description                                                                                                                                                                                                                                                                                             |

| Mass Storage<br>Hardware Vendor<br>Publications | Series 540 Cartridge Tape Drive Product Description, Cipher Data<br>Products, Inc., Bulletin Number 01-311-0284-1K (¼-inch tape drive)                                                                                                                                                                                                          |

| Optional Equipment<br>Hardware<br>Publications  | Explorer NuBus Ethernet® Controller General Description       2243161-0001         Model 855 Printer Operator's Manual       2225911-0001         Model 855 Printer Technical Reference Manual       2232822-0001         Model 855/856 Printer Maintenance Manual       2225914-0001                                                           |

Explorer and NuBus are trademarks of Texas Instruments Incorporated. Ethernet is a registered trademark of Xerox Corporation.

## THE EXPLORER<sup>™</sup>SYSTEM SOFTWARE MANUALS

| Mastering the                |                                                          |              |

|------------------------------|----------------------------------------------------------|--------------|

| Explorer                     | Explorer Technical Summary                               |              |

| Environment                  | Explorer Operations Guide                                |              |

| Environment                  | Explorer Zmacs Editor Tutorial                           |              |

|                              | Explorer Glossary                                        |              |

|                              | Explorer Communications User's Guide                     |              |

|                              | Explorer Diagnostics                                     |              |

|                              | Explorer Master Index to Software Manuals                |              |

|                              | Explorer System Software Installation                    |              |

| Programming With             |                                                          | <del></del>  |

|                              | Explorer Programming Primer                              |              |

| the Explorer                 | Common LISP, The Language, by Guy L. Steele, Jr.         |              |

|                              | Explorer Lisp Reference                                  |              |

|                              | Explorer Zmacs Editor Reference                          |              |

|                              | Explorer Programming Concepts and Tools                  |              |

|                              | Explorer Window System Reference                         |              |

|                              | Explorer Command Interface Toolkit User's Guide          |              |

|                              |                                                          |              |

| Explorer Toolkits            | Explorer Natural Language Menu System User's Guide       |              |

|                              | Explorer Relational Table Management System User's Guide |              |

|                              | Explorer Graphics Toolkit User's Guide                   | 2243195-0001 |

|                              | Explorer Grasper User's Guide                            | 2243135-0001 |

|                              | Explorer Prolog Toolkit User's Guide                     | 2243204-0001 |

|                              | Programming in Prolog, by Clocksin and Mellish           |              |

|                              | Explorer Color Graphics User's Guide, Support for the    |              |

|                              | Raster Technologies Model One                            |              |

|                              | Explorer TCP/IP User's Guide                             |              |

|                              |                                                          |              |

| System Software<br>Internals | Explorer System Software Design Notes                    |              |

Explorer is a trademark of Texas Instruments Incorporated.

### **ABOUT THIS MANUAL**

| Introduction               | This document describes the memory board used in the Texas Instruments<br>Explorer computer system. The intended audience for this document<br>includes original equipment manufacturers (OEMs), system designers, field<br>maintenance personnel, TI customer representatives, and people in similar<br>groups. |

|----------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Contents of<br>This Manual | This document consists of four sections. A brief description of each section is as follows:                                                                                                                                                                                                                      |

|                            | <b>Section 1:</b> Introduction — Provides general information on the Explorer memory board.                                                                                                                                                                                                                      |

|                            | <b>Section 2:</b> Installation — Provides unpacking, installation, and removal procedures for the memory board.                                                                                                                                                                                                  |

|                            | <b>Section 3:</b> Operating Instructions — Provides self-test operating instructions for the memory board.                                                                                                                                                                                                       |

|                            | <b>Section 4:</b> System Design and Programming Data — Provides a block diagram description of the memory board, a general description of the local bus and NuBus data transfers, and programming information.                                                                                                   |

|                            |                                                                                                                                                                                                                                                                                                                  |

## CONTENTS

|   | Paragraph                                                                                                                                     | Title                                                                                                                                                                                                                                                                                                                                                                                    | Page               |

|---|-----------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|

| 1 |                                                                                                                                               | Introduction                                                                                                                                                                                                                                                                                                                                                                             |                    |

| - | 1.1                                                                                                                                           | General                                                                                                                                                                                                                                                                                                                                                                                  | 1-3                |

|   | 1.2                                                                                                                                           | Features                                                                                                                                                                                                                                                                                                                                                                                 |                    |

|   | 1.3                                                                                                                                           | Specifications                                                                                                                                                                                                                                                                                                                                                                           |                    |

|   | 1.4                                                                                                                                           | Performance                                                                                                                                                                                                                                                                                                                                                                              |                    |

|   | 1.4.1                                                                                                                                         | Board Clock Frequency                                                                                                                                                                                                                                                                                                                                                                    |                    |

|   | 1.4.2                                                                                                                                         | Amount of Bus Arbitration                                                                                                                                                                                                                                                                                                                                                                |                    |

|   | 1.4.3                                                                                                                                         | Memory Access From the Local Bus                                                                                                                                                                                                                                                                                                                                                         |                    |

|   | 1.4.4                                                                                                                                         | Memory Access From the NuBus                                                                                                                                                                                                                                                                                                                                                             |                    |

| 2 |                                                                                                                                               | Installation                                                                                                                                                                                                                                                                                                                                                                             |                    |

|   | 2.1                                                                                                                                           | Introduction                                                                                                                                                                                                                                                                                                                                                                             | 2-3                |

|   | 2.2                                                                                                                                           | Unpacking Procedure                                                                                                                                                                                                                                                                                                                                                                      | 2-3                |

|   | 2.3                                                                                                                                           | Installation and Removal Procedure                                                                                                                                                                                                                                                                                                                                                       | 2-5                |

| 3 |                                                                                                                                               | Operating Instructions                                                                                                                                                                                                                                                                                                                                                                   |                    |

|   | 3.1                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                          | 3-3                |

|   | 3.2                                                                                                                                           | Self-Test Procedures                                                                                                                                                                                                                                                                                                                                                                     |                    |

|   |                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                          |                    |

| 4 |                                                                                                                                               | System Design and Programming Data                                                                                                                                                                                                                                                                                                                                                       |                    |

| 4 | 4.1                                                                                                                                           | System Design and Programming Data Introduction                                                                                                                                                                                                                                                                                                                                          | 4-3                |

| 4 | 4.1<br>4.2                                                                                                                                    | Introduction                                                                                                                                                                                                                                                                                                                                                                             |                    |

| 4 |                                                                                                                                               | Introduction<br>Block Diagram Description                                                                                                                                                                                                                                                                                                                                                | 4-4                |

| 4 | 4.2                                                                                                                                           | Introduction<br>Block Diagram Description<br>Module Slot Addressing                                                                                                                                                                                                                                                                                                                      | 4-4<br>4-6         |

| 4 | 4.2<br>4.2.1                                                                                                                                  | Introduction<br>Block Diagram Description<br>Module Slot Addressing<br>Base Address Register                                                                                                                                                                                                                                                                                             |                    |

| 4 | 4.2<br>4.2.1<br>4.2.2                                                                                                                         | Introduction<br>Block Diagram Description<br>Module Slot Addressing<br>Base Address Register<br>NuBus Structure                                                                                                                                                                                                                                                                          |                    |

| 4 | 4.2<br>4.2.1<br>4.2.2<br>4.2.3                                                                                                                | Introduction<br>Block Diagram Description<br>Module Slot Addressing<br>Base Address Register<br>NuBus Structure<br>Data Transfer Mode Signals                                                                                                                                                                                                                                            |                    |

| 4 | 4.2<br>4.2.1<br>4.2.2<br>4.2.3<br>4.2.4                                                                                                       | Introduction<br>Block Diagram Description<br>Module Slot Addressing<br>Base Address Register<br>NuBus Structure<br>Data Transfer Mode Signals<br>NuBus Status Code Signals                                                                                                                                                                                                               |                    |

| 4 | $\begin{array}{c} 4.2 \\ 4.2.1 \\ 4.2.2 \\ 4.2.3 \\ 4.2.4 \\ 4.2.5 \\ 4.2.6 \end{array}$                                                      | Introduction<br>Block Diagram Description<br>Module Slot Addressing<br>Base Address Register<br>NuBus Structure<br>Data Transfer Mode Signals<br>NuBus Status Code Signals<br>NuBus Block Sizes and Starting Addresses                                                                                                                                                                   |                    |

| 4 | $\begin{array}{c} 4.2\\ 4.2.1\\ 4.2.2\\ 4.2.3\\ 4.2.4\\ 4.2.5\\ 4.2.6\\ 4.2.7\end{array}$                                                     | Introduction<br>Block Diagram Description<br>Module Slot Addressing<br>Base Address Register<br>NuBus Structure<br>Data Transfer Mode Signals<br>NuBus Status Code Signals<br>NuBus Block Sizes and Starting Addresses.<br>Clock Generation                                                                                                                                              |                    |

| 4 | $\begin{array}{c} 4.2\\ 4.2.1\\ 4.2.2\\ 4.2.3\\ 4.2.4\\ 4.2.5\\ 4.2.6\\ 4.2.7\\ 4.2.8\end{array}$                                             | Introduction<br>Block Diagram Description<br>Module Slot Addressing<br>Base Address Register<br>NuBus Structure<br>Data Transfer Mode Signals<br>NuBus Status Code Signals<br>NuBus Block Sizes and Starting Addresses<br>Clock Generation<br>Bus Arbitration Logic                                                                                                                      |                    |

| 4 | $\begin{array}{c} 4.2\\ 4.2.1\\ 4.2.2\\ 4.2.3\\ 4.2.4\\ 4.2.5\\ 4.2.6\\ 4.2.7\\ 4.2.8\\ 4.2.9\end{array}$                                     | Introduction<br>Block Diagram Description<br>Module Slot Addressing<br>Base Address Register<br>NuBus Structure<br>Data Transfer Mode Signals<br>NuBus Status Code Signals<br>NuBus Status Code Signals<br>NuBus Block Sizes and Starting Addresses<br>Clock Generation<br>Bus Arbitration Logic<br>NuBus Arbitration                                                                    |                    |

| 4 | $\begin{array}{c} 4.2\\ 4.2.1\\ 4.2.2\\ 4.2.3\\ 4.2.4\\ 4.2.5\\ 4.2.6\\ 4.2.7\\ 4.2.8\\ 4.2.9\\ 4.2.10\end{array}$                            | Introduction<br>Block Diagram Description<br>Module Slot Addressing<br>Base Address Register<br>NuBus Structure<br>Data Transfer Mode Signals<br>NuBus Status Code Signals<br>NuBus Block Sizes and Starting Addresses.<br>Clock Generation<br>Bus Arbitration Logic<br>NuBus Arbitration<br>Control Logic                                                                               |                    |

| 4 | $\begin{array}{c} 4.2\\ 4.2.1\\ 4.2.2\\ 4.2.3\\ 4.2.4\\ 4.2.5\\ 4.2.6\\ 4.2.7\\ 4.2.8\\ 4.2.9\\ 4.2.10\\ 4.2.11\end{array}$                   | Introduction<br>Block Diagram Description<br>Module Slot Addressing<br>Base Address Register<br>NuBus Structure<br>Data Transfer Mode Signals<br>NuBus Status Code Signals<br>NuBus Block Sizes and Starting Addresses.<br>Clock Generation<br>Bus Arbitration Logic<br>NuBus Arbitration<br>Control Logic<br>Local Bus and NuBus Locking.                                               | $\begin{array}{c}$ |

| 4 | $\begin{array}{c} 4.2\\ 4.2.1\\ 4.2.2\\ 4.2.3\\ 4.2.4\\ 4.2.5\\ 4.2.6\\ 4.2.7\\ 4.2.8\\ 4.2.9\\ 4.2.10\\ 4.2.11\\ 4.2.12\end{array}$          | Introduction<br>Block Diagram Description<br>Module Slot Addressing<br>Base Address Register<br>NuBus Structure<br>Data Transfer Mode Signals<br>NuBus Status Code Signals<br>NuBus Block Sizes and Starting Addresses.<br>Clock Generation<br>Bus Arbitration Logic<br>NuBus Arbitration<br>Control Logic<br>Local Bus and NuBus Locking.<br>Jumper Options                             | $\begin{array}{c}$ |

| 4 | $\begin{array}{c} 4.2\\ 4.2.1\\ 4.2.2\\ 4.2.3\\ 4.2.4\\ 4.2.5\\ 4.2.6\\ 4.2.7\\ 4.2.8\\ 4.2.9\\ 4.2.10\\ 4.2.11\\ 4.2.12\\ 4.2.13\end{array}$ | Introduction<br>Block Diagram Description<br>Module Slot Addressing<br>Base Address Register<br>NuBus Structure<br>Data Transfer Mode Signals<br>NuBus Status Code Signals<br>NuBus Block Sizes and Starting Addresses<br>Clock Generation<br>Bus Arbitration Logic<br>NuBus Arbitration<br>Control Logic<br>Local Bus and NuBus Locking<br>Jumper Options<br>Memory Address Development | $\begin{array}{c}$ |

| 4 | $\begin{array}{c} 4.2\\ 4.2.1\\ 4.2.2\\ 4.2.3\\ 4.2.4\\ 4.2.5\\ 4.2.6\\ 4.2.7\\ 4.2.8\\ 4.2.9\\ 4.2.10\\ 4.2.11\\ 4.2.12\end{array}$          | Introduction<br>Block Diagram Description<br>Module Slot Addressing<br>Base Address Register<br>NuBus Structure<br>Data Transfer Mode Signals<br>NuBus Status Code Signals<br>NuBus Block Sizes and Starting Addresses.<br>Clock Generation<br>Bus Arbitration Logic<br>NuBus Arbitration<br>Control Logic<br>Local Bus and NuBus Locking.<br>Jumper Options                             | $\begin{array}{c}$ |

# INTRODUCTION

Highlights of ■ This Section

- General information

- Features

- Specifications

- Performance

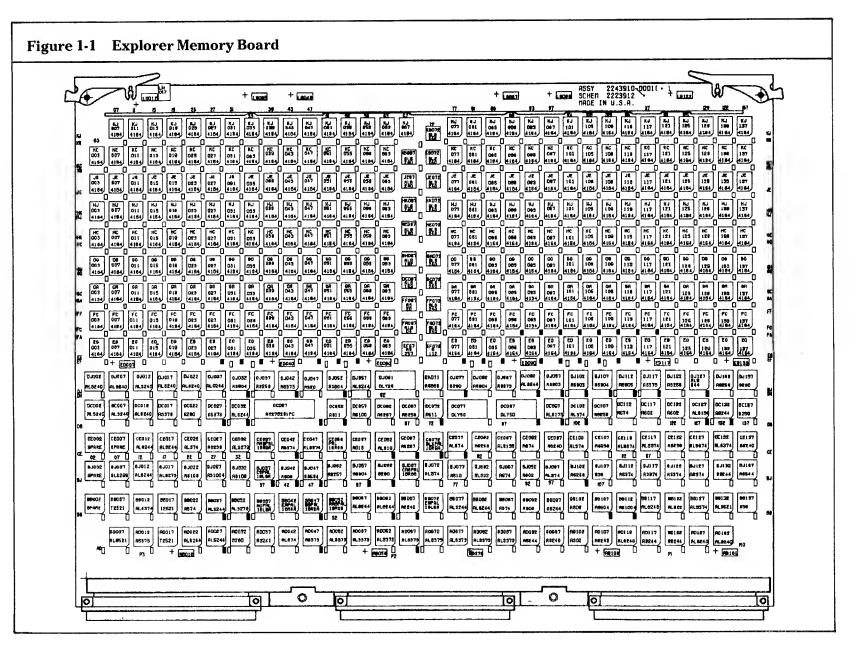

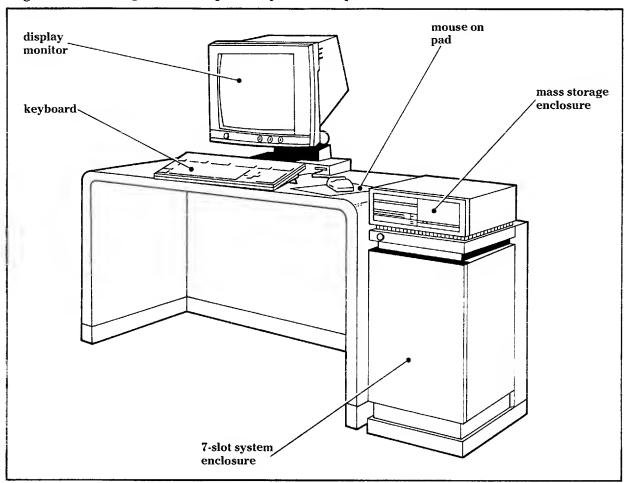

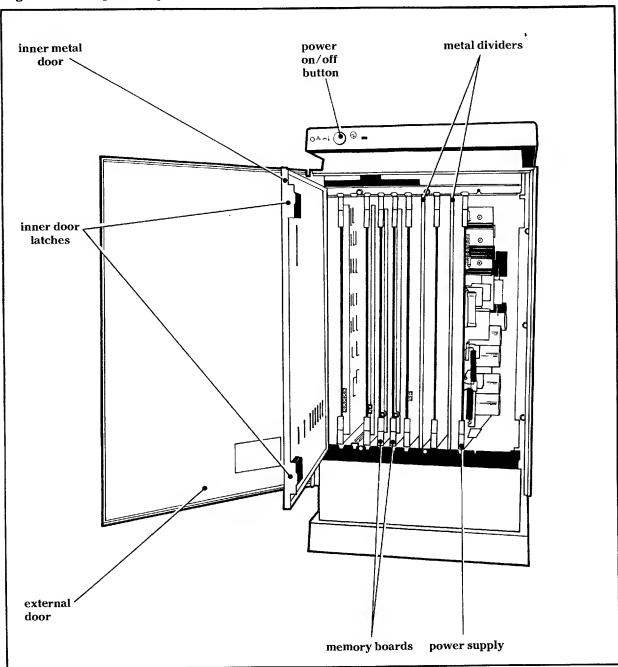

#### **General** 1.1 This section provides general information on the Explorer memory board shown in Figure 1-1. The components of an Explorer computer system are shown in Figure 1-2. Figure 1-3 shows the system enclosure in more detail.

The memory board is a standard three-high Eurocard design with three standard DIN connectors referred to as P1, P2, and P3. The expression Eurocard indicates a European mechanical-design standard for circuit boards. The number of connectors a board has space for indicates the height of the board. For example, a one-high Eurocard has space for one connector and is 100 millimeters (3.9 inches) high and 280 millimeters (11 inches) in depth. A three-high Eurocard has space for three connectors and is 366.7 millimeters (14.4 inches) high. All Eurocards have the same depth. In addition, the memory board has special ejector/injector mechanisms that provide easy insertion and removal of the board from the mating connectors on the backplane of the system enclosure.

The memory board has a capacity of two megabytes when using 64K-bit (where K equals 1024) dynamic random-access memory (DRAM) chips, and a capacity of eight megabytes when equipped with 256K-bit DRAM chips. Explorer memory boards are also available in one-megabyte and four-megabyte capacities.

Memory General Description

Figure 1-2 Example of the Explorer System Components

Figure 1-3 Explorer System Enclosure

The memory board communicates with other components in the system over the local bus and the NuBus communication paths. The NuBus is a high-speed synchronous bus that multiplexes 32-bit data words with 32-bit address codes. It has a simple communications protocol that allows the circuit boards on the bus to be master or slave devices over the bus. The local bus is also a high-speed synchronous bus, but it provides separate paths for the 32-bit data words and 32-bit address codes. The memory board contains the circuits that allow the processor on the local bus to communicate with the NuBus as a master or slave.

Although some of the circuit boards can be inserted in any slot in the system enclosure, there are certain boards that should always be located in particular slots. A typical board configuration is as follows:

- Slot 0 NuBus Ethernet controller board (if Ethernet is present)

- Slot 1 Optional slot

- Slot 2 NuBus peripheral interface (NUPI) board

- Slot 3 Memory board

- Slot 4 Memory board

- Slot 5 System interface board (SlB)

- Slot 6 Processor board

- Slot 7 Power supply

The assigned slots are:

- Slot 6 is reserved for the processor board.

- Slot 5 should contain the system interface board to keep it close to the processor.

- Slot 4 must contain a memory board, which becomes the master memory board when two or more are present.

Slots 0, 1, 2, and 3 are nonrestrictive; that is, any of the boards not assigned to slots 4, 5, and 6 can be located in any of the remaining slots.

The slots are identified by a 4-bit identification (ID) code that represents hexadecimal numbers 0 through F on the backplane. This ID code becomes part of the board address configuration when the board is inserted into a slot. The board slot address configuration is:

>FSXXXXXX

where:

F is a hexadecimal value. S is the slot 1D. X is a variable, 0 through F.

A configuration read-only memory (ROM) is provided on each circuit board. This ROM contains a unique name to identify the specific board of which it is a part. This name is addressed along with the slot ID during power-up so that the processor knows the type of circuit board in each slot during all succeeding address operations on the NuBus and the local bus.

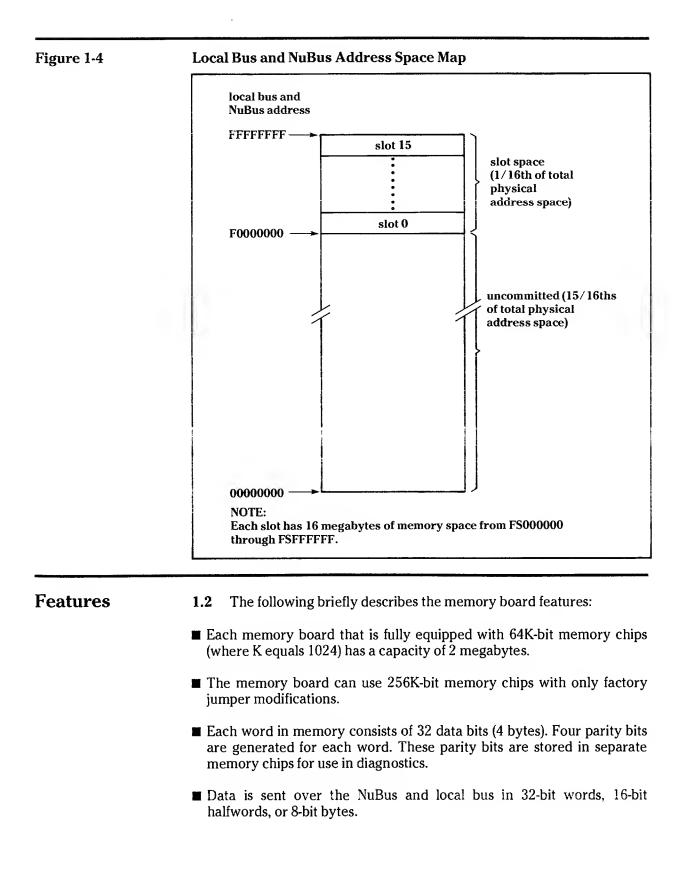

Each slot has 16 megabytes of address space from >FS000000 through >FSFFFFF. These address spaces are distributed to the 16 possible slots on the address space map shown in Figure 1-4. The 16 slots allow a total address capacity of 256 megabytes. This is only 1/16th of the total address capacity of the full 32-bit NuBus and local bus, which is 4 gigabytes. The unused address space is uncommitted and allocated as required.

The local bus uses only four slots on the Explorer system enclosure, which limits the address capacity to 64 megabytes. The local bus has the capacity to address four gigabytes when using the full 32-bit address and the base register feature that allows for memory address mapping.

- The memory board provides a communication interface to the NuBus and the local bus.

- The memory space can be accessed from either the NuBus or the local bus.

- The memory board is a slave to the NuBus except when the local bus processor has control of the memory board. The memory board can then become the NuBus master by arbitrating for NuBus control.

- The memory board is always a slave to the local bus when the local bus is provided.

- When two memory boards are used in a system with a NuBus and a local bus, one board can access the NuBus at the same time the other board is accessing the local bus.

- The slot address of the memory board is determined by four ID bits on the NuBus that are connected to ground at each connector to make the ID code for that slot.

- The memory board contains a base register that allows data from the NuBus or the local bus to change the address range of the memory board.

- Memory data block transfers are supported when the memory board is functioning as a NuBus slave. Block transfers are not supported on the local bus.

- The memory board provides a locking circuit that can lock out the NuBus or the local bus so that either bus can perform continuous read/write cycles.

- The memory board uses the clock signals from the NuBus and local bus. The NuBus clock must be available at all times. Most circuitry is synchronized with a board clock which is driven by the clock for the bus which is currently accessing the memory board.

#### **Specifications** 1.3 Table 1-1 lists the general specifications for the Explorer memory board. **Memory Board Specifications** Table 1-1 Item **Specifications** Power usage: Voltage 5 Vdc 9.5 A (with 2 megabytes) Typical current 10.1 A (with 8 megabytes) Ambient temperature: 10 to 35° C (50 to 95° F) Operating Nonoperating -40 to $65^{\circ}$ C (-40 to $149^{\circ}$ F) Relative humidity:

Operating 15 to 80% noncondensing Nonoperating 5 to 95% noncondensing **Dimensions:** Width 366.7 mm (14.437 in) 280 mm (11.024 in) Depth 18.11 mm (0.714 in) maximum Thickness (with components) 2 megabytes (with 64K-bit chips) Memory capacity (maximum) 8 megabytes (with 256K-bit chips) Logic states: Unasserted (high false) >2.0 V at the receiver Asserted (low true) < 0.8 V at the receiver 7 to 10 MHz (processor determined) Local bus clock frequency 10 MHz NuBus clock frequency Electromagnetic emission Complies with FCC level B, EMI/RFI office emission requirements

Memory General Description

| Performance                         | 1.4 The performance characteristics of the Explorer memory board are explained in the following paragraphs.                                                                                                                                                                                                             |  |

|-------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Board Clock<br>Frequency            | <b>1.4.1</b> The board clock can be driven from the local bus at a frequency from 7 to 10 megahertz, or it can be driven from the NuBus at a frequency of 10 megahertz.                                                                                                                                                 |  |

| Amount of<br>Bus Arbitration        | <b>1.4.2</b> The memory board selects the NuBus after initial power-up or NuBus board reset. After that the last bus to access the memory board remains selected. Time spent in selecting and enabling the requesting bus, if necessary, is approximately equal to one memory access time (four or five clock periods). |  |

|                                     | Simultaneous requests for memory access from the local bus and the<br>NuBus result in the selection of the competing bus after each access, until<br>only one bus is left with a request. This allows equal access to either bus;<br>however, it results in bus selection time between accesses.                        |  |

|                                     | The information in the following two paragraphs explains the access times, assuming that the memory board is already synchronized to the requesting bus.                                                                                                                                                                |  |

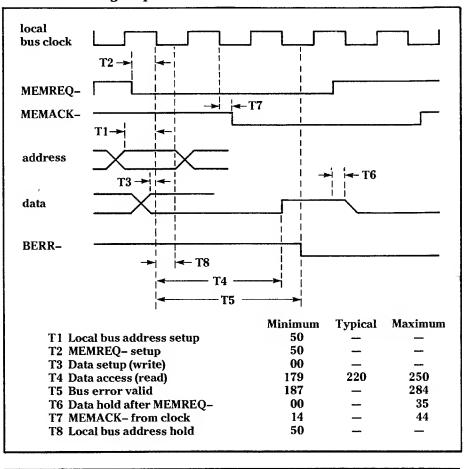

| Memory Access<br>From the Local Bus | <b>1.4.3</b> In memory read operations, data is valid 250 nanoseconds after the falling edge of the local bus clock. BERR is valid 284 nanoseconds after the same falling edge.                                                                                                                                         |  |

|                                     | In memory write operations, MEMREQ- must be held asserted until two clock periods after the falling edge of the local bus clock. Data and address line values are irrelevant 50 nanoseconds after the first falling edge of the local bus clock.                                                                        |  |

| Memory Access<br>From the NuBus     | <b>1.4.4</b> In single memory read operations, data and control lines are valid on the fifth sample edge after the START– signal.                                                                                                                                                                                       |  |

|                                     | In single memory write operations, data and control lines are valid on the fourth sample edge after the START- signal.                                                                                                                                                                                                  |  |

|                                     | In block memory read operations, data and control lines are valid on the fifth sample edge and on every third sample edge after that until the completion of a transfer.                                                                                                                                                |  |

|                                     | In block memory write operations, data and control lines are valid on the fourth sample edge and on every other sample edge after that until the completion of a transfer.                                                                                                                                              |  |

١

| Paragraph | Title                                             | Page |

|-----------|---------------------------------------------------|------|

| 4.3       | Data Transfer Operation                           | 4-25 |

| 4.3.1     | Single Data Cycle Transaction                     |      |

| 4.3.1.1   | Read/Write Transaction                            |      |

| 4.3.1.2   | Idle Cycle Operations                             |      |

| 4.3.1.3   | Acknowledgment                                    |      |

| 4.3.2     | Block Data Transfers                              |      |

| 4.3.2.1   | Block Read/Write Transactions                     |      |

| 4.3.2.2   | Block Transfer Errors                             |      |

| 4.3.3     | Interrupt Operations                              |      |

| 4.4       | Programming Information                           |      |

| 4.4.1     | Control Address Space                             |      |

| 4.5       | Configuration ROM Description                     |      |

| 4.5.1     | Configuration Register                            |      |

| 4.5.2     | Base Register                                     |      |

| 4.5.3     | Failure Location Latch and Test Register          |      |

| 4.5.3.1   | Reading Failure Location Information              |      |

| 4.5.3.2   | Writing Parity Test Bits                          |      |

| 4.5.4     | NuBus Termination Status and Error Latch Register |      |

### Glossary

#### Index

|           | Figure | Title                                             | Page |  |

|-----------|--------|---------------------------------------------------|------|--|

| Figures   | 1-1    | Explorer Memory Board                             | 1-4  |  |

| - igui co | 1-2    | Example of the Explorer System Components         |      |  |

|           | 1-3    | Explorer System Enclosure                         |      |  |

|           | 1-4    | Local Bus and NuBus Address Space Map             |      |  |

|           | 2-1    | Memory Board in Packing Container                 | 2-4  |  |

|           | 2-2    | Removal of Static-Protective Bag                  |      |  |

|           | 3-1    | Fault LED Locations                               | 3-4  |  |

|           | 4-1    | Memory Board Physical Organization                | 4-3  |  |

|           | 4-2    | Memory Board Block Diagram                        |      |  |

|           | 4-3    | Full 32-Bit Address Configuration                 |      |  |

|           | 4-4    | NuBus Bit Organization                            |      |  |

|           | 4-5    | Data Paths for Bytes, Halfwords and Words         |      |  |

|           | 4-6    | Board Clock Regeneration From the Local Bus Clock |      |  |

|           | 4-7    | Board Clock Regeneration From the NuBus Clock     |      |  |

|           | 4-8    | Single Cycle and Block Transaction Comparisons    |      |  |

|           | 4-9    | Local Bus Timing Requirements                     | 4-26 |  |

| Title                                             | Figure                                                                                                    |

|---------------------------------------------------|-----------------------------------------------------------------------------------------------------------|

| Configuration Register Contents                   | 4-10                                                                                                      |

|                                                   |                                                                                                           |

|                                                   |                                                                                                           |

|                                                   |                                                                                                           |

| NuBus Termination Status and Error Latch Register |                                                                                                           |

|                                                   | Configuration Register Contents<br>Base Register Contents<br>Failure Latch Byte<br>Test Register Contents |

### Table Title

### Page

| Tables | 1-1  | Memory Board Specifications                   | 1-10 |

|--------|------|-----------------------------------------------|------|

|        | 4-1  | NuBus Slot Number/iD Code Assignments         | 4-6  |

|        | 4-2  | Data Transfer Mode Signals                    |      |

|        | 4-3  | NuBus Status Code Summary                     |      |

|        | 4-4  | NuBus Block Sizes and Starting Addresses      |      |

|        | 4-5  | Jumpers for 64K-Bit and 256K-Bit chips        |      |

|        | 4-6  | Address Development for 64K-Bit Memory Chips  | 4-16 |

|        | 4-7  | Address Development for 256K-Bit Memory Chips |      |

|        | 4-8  | Local Bus Signal Definitions                  |      |

|        | 4-9  | NuBus Signal Definitions                      |      |

|        | 4-10 | Additional Explorer Signal Definitions        |      |

|        | 4-11 | NuBus Connector P1 Signals                    |      |

|        | 4-12 | Local Bus Connector P2 Signals                |      |

|        | 4-13 | I/O Connector P3 Signals                      |      |

|        | 4-14 | Configuration ROM Contents                    |      |

|        |      | -                                             |      |

# INSTALLATION

Highlights of Introduction This Section

- Unpacking procedure

- Installation and removal procedure

| Introduction | <ul> <li>2.1 This section provides unpacking, installation, and removal instructions for the Explorer memory board.</li> <li>CAUTION: The memory board contains static-sensitive electronic components. To prevent damage to these components, make sure that you are properly grounded before handling the memory board.</li> </ul> |                                                                                                                                                                                                                                                 |  |

|--------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

|              |                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                 |  |

|              | Before storing or transporting the memory board, return it to its static-protective package or the system enclosure.                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                 |  |

|              | Unpacking<br>Procedure                                                                                                                                                                                                                                                                                                               | <ul><li>2.2 Unpack and visually check the memory board as follows:</li><li>1. Check for any documents fastened to the exterior of the packing container. If any documents are found, read and follow the instructions that are given.</li></ul> |  |

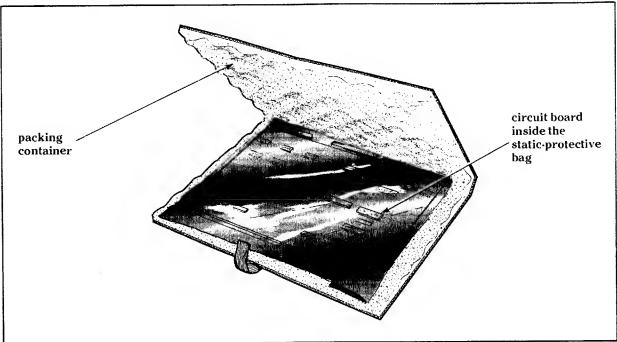

2. Open the packing container (Figure 2-1) and carefully remove the packing material; then remove the memory board with the static-protective bag in place.

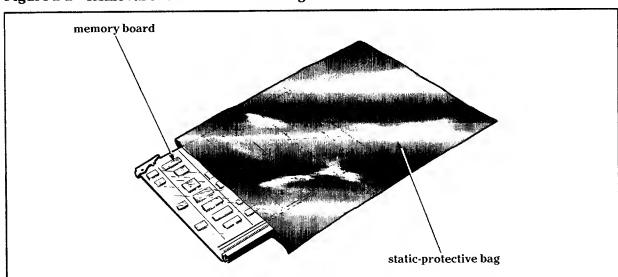

- 3. Remove the static-protective bag (Figure 2-2) from the memory board. Be sure to follow the static-caution recommendations when handling the memory board without the static-protective bag.

- 4. Check the memory board for scratches, broken parts, marred finish, or any other damage that may have occurred during shipment. Follow your local procedures to report any damage.

Figure 2-2 Removal of Static-Protective Bag

- Installation and Removal Procedure

- 2.3 Install or remove a memory board as follows:

**NOTE:** There are no jumpers or switches to set or check prior to installing the memory board.

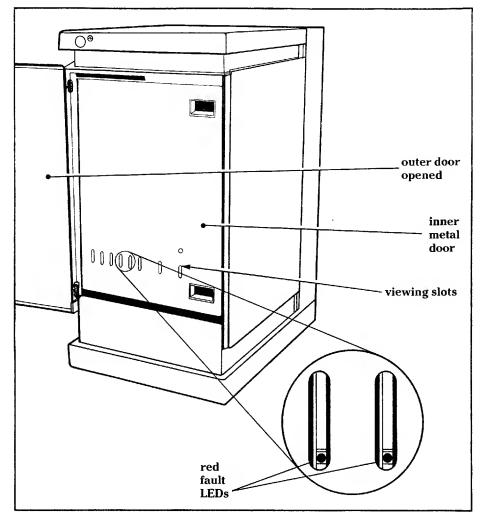

- 1. Set the power switch on the system enclosure to the off position. The power on/off switch is a pushbutton at the upper left-hand corner of the front of the system enclosure. The in position is on, the out position is off.

- 2. Open the front door of the system enclosure.

- 3. Release the latches on the internal metal door, and open this door.

- 4. Slide the memory board into the proper slot and into the connectors on the backplane. Lock the board into the slot connectors on the backplane using the two injector/ejectors on the ends of the board. The injector/ejectors are also used to remove the board from the backplane connectors.

**NOTE:** To remove the board, follow steps 1 through 4 except in step 4 slide the board out of the slot instead of into the slot.

- 5. If you are ready to switch on the system, leave the outer door ajar so you can see the fault indicator light emitting diodes (LEDs) near the edges of the circuit boards. For power-up and self-test procedures, please refer to Section 3.

- 6. After the self-tests are completed and you are ready for routine operation, close the front door of the system enclosure.

### **OPERATING INSTRUCTIONS**

Highlights of<br/>This SectionThis section describes system start-up procedures, the self-tests that occur<br/>automatically, and the meaning of red fault LEDs going off or staying on.

| Introduction            | <b>3.1</b> This section describes the memory board self-tests that occur automatically when power is first applied to the system.                                                                                                                                                                                                                                                                                                                                                                |

|-------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Self-Test<br>Procedures | <b>3.2</b> When power is first applied to the Explorer system, a number of self-tests occur automatically. The results of these self-tests are shown on the video display as they are completed. The automatic self-test does not test the entire memory board, but an extended self-test is available which does. This is mentioned at the appropriate point in the self-test procedure that follows:                                                                                           |

|                         | WARNING: Except during the self-test period when the front door<br>is left open to observe the fault LEDs, do not operate the computer<br>system with doors and/or panels of the system enclosure open.<br>Under normal conditions, interlocks prevent power from being<br>applied when these panels are not in place and the inner metal door<br>is open. Do not bypass or otherwise tamper with the interlocks.<br>Potentially lethal voltages are exposed if this warning is not<br>observed. |

|                         | <ol> <li>Set the power switch to the on (in) position. The power on/off switch is<br/>a pushbutton near the upper left-hand corner of the front of the system<br/>enclosure.</li> </ol>                                                                                                                                                                                                                                                                                                          |

|                         | 2. Check the red fault LEDs on the circuit boards in the system enclosure while the self-tests are running. The fault LEDs are located at the lower front edges of the boards, as shown in Figure 3-1.                                                                                                                                                                                                                                                                                           |

|                         | 3. The self-test microcode on the processor board runs first. If the red fault LED on the processor board goes out, the processor board is good. The self-tests on the processor board then run the self-test microcode on the memory board.                                                                                                                                                                                                                                                     |

|                         | <ol><li>If the red fault LED on a memory board goes out, the memory board is good.</li></ol>                                                                                                                                                                                                                                                                                                                                                                                                     |

|                         | <ol><li>If the red fault LED on a memory board remains on after the self-test,<br/>the board is probably faulty.</li></ol>                                                                                                                                                                                                                                                                                                                                                                       |

|                         | <ol> <li>The automatic self-test does not test the entire memory board. Before<br/>proceeding further, you may want to press the E key to run the<br/>extended mode self-tests.</li> </ol>                                                                                                                                                                                                                                                                                                       |

#### Figure 3-1

**Fault LED Locations**

- 7. If the memory board in slot 4 fails, it can be temporarily replaced with the board from slot 3. (There must be a good memory board in slot 4 for the system to operate.) If the memory board in slot 3 fails, it can be laid aside until a replacement is available. The system can be used, but with a reduced amount of memory, as long as a good memory board is located in slot 4.

- 8. If the red fault LEDs on the processor board and the memory board remain on, then a fault may exist on the processor board, memory board, or other system component.

- 9. Refer to the installation and removal procedure in Section 2 to replace the faulty board.

### SYSTEM DESIGN AND PROGRAMMING DATA

Highlights of Introduction This Section

- Block diagram description

- Data transfer operation

- Programming information

# **Introduction 4.1** This section provides general operating and design information for the Explorer memory board under the following topics:

- Block diagram description

- Data transfer operation

- Programming information

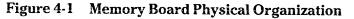

Figure 4-1 shows the physical organization of the components on the memory board. There are eight rows of memory chips defined as rows 00 through 07, with one row provided for parity. Each memory and parity row contains 32 memory chips. The memory rows are divided into four groups of 8 chips. The four groups are then defined as bytes 00 through 03, indicating the 4 bytes of a 32-bit word. Using 64K-bit chips, there are 256K bytes per row of chips, providing 2 megabytes of memory in eight rows. Using 256K-bit chips, there is 1 megabyte per row of chips, providing 8

Memory General Description

System Design and Programming Data 4-3

megabytes of memory in eight rows. The boards can also be half equipped with chips, which allow memory capacities of 1 megabyte and 4 megabytes.

The other logic on the board includes drivers, control logic, a configuration read-only memory (ROM), and local bus and NuBus buffers and drivers. The memory board also has one self-test fault LED, three connectors defined as P1, P2, and P3, and two board ejector/injector devices.

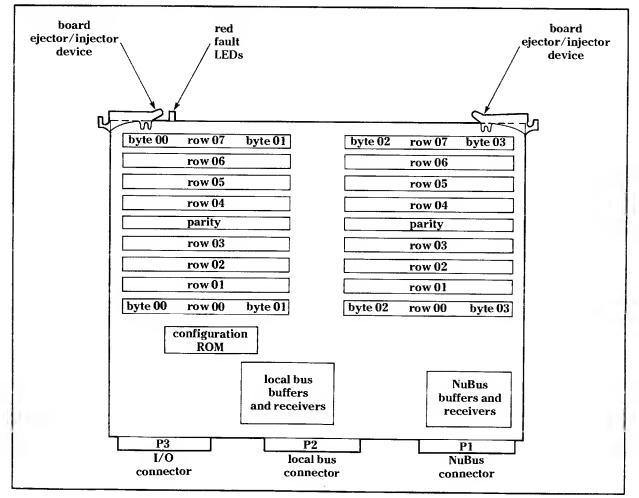

# Block Diagram4.2Use the memory board block diagram (Figure 4-2) as a guide in the<br/>analysis of the following memory board operations:

- Module slot addressing

- Base address register

- Organization of words, halfwords, and bytes

- Data transfer mode signals

- NuBus status code signals

- NuBus block sizes and starting addresses

- Clock generation

- Bus arbitration logic

- NuBus arbitration

- Control logic

- Local bus and NuBus locking

- Jumper options

- Memory address development

- Memory refresh cycle

- Local bus and NuBus signal definitions

- Connector pin/signal assignments

Memory General Description

System Design and Programming Data 4-5

#### Module Slot Addressing

**4.2.1** The memory board contains the NuBus master interface for the processor on the local bus. The NuBus master interface is enabled by the BS0– signal that is connected only to slot 4 on the local bus backplane in the system enclosure. The memory board in slot 4 is then the NuBus master for the processor on the local bus when BS0– is asserted. When there are two memory boards in a chassis with a NuBus and a local bus, one board can service the NuBus at the same time the other board is servicing the local bus.

The slot address of the memory board is determined by the four ID(3:0)bits on the backplane that are related to the slots on the NuBus as shown in Table 4-1. Asserted bits in the hexadecimal ID(3:0)- code are connected to ground. For example, hexadecimal code F has all four bits connected to ground, and none of the four bits in hexadecimal code 0 are connected to ground.

| Table 4-1 | NuBus Slot Number/ID (           | Code Assignments |  |

|-----------|----------------------------------|------------------|--|

|           | Hexadecimal<br>ID 10(3:0) – Code | Slot<br>Number   |  |

|           | 0                                | 0                |  |

|           | 1                                | 1                |  |

|           | 2                                | 2                |  |

|           | 3                                | 3                |  |

|           | 4                                | 4                |  |

|           | 5                                | 5                |  |

|           | 6                                | 6                |  |

|           | 7                                | 7                |  |

|           | 8                                | 8                |  |

|           | 9                                | 9                |  |

|           | А                                | 10               |  |

|           | В                                | 11               |  |

|           | С                                | 12               |  |

|           | D                                | 13               |  |

|           | Ē                                | 14               |  |

|           | F                                | 15               |  |

#### NOTE:

Slots are numerically listed from left to right as viewed from the front of the system enclosure. Although the Explorer system enclosure uses only seven addressable slots, the slot IDs can accommodate up to 16 addressable slots.

A reference to any address >FSXXXXX will select the memory board. Addresses starting at >FSFFFFF and decreasing through >FSFFC000 make up the control area and contain the configuration ROM and the onboard registers. Memory data addresses for the different sizes of memory boards are as follows:

#### Memory Size Memory Data Addresses

| 1 megabyte  | >FS000000 through >FS0FFFFF |

|-------------|-----------------------------|

| 2 megabytes | >FS000000 through >FS1FFFFF |

| 4 megabytes | >FS000000 through >FS3FFFFF |

| 8 megabytes | >FS000000 through >FS7FFFFF |

|             |                             |

#### Base Address Register

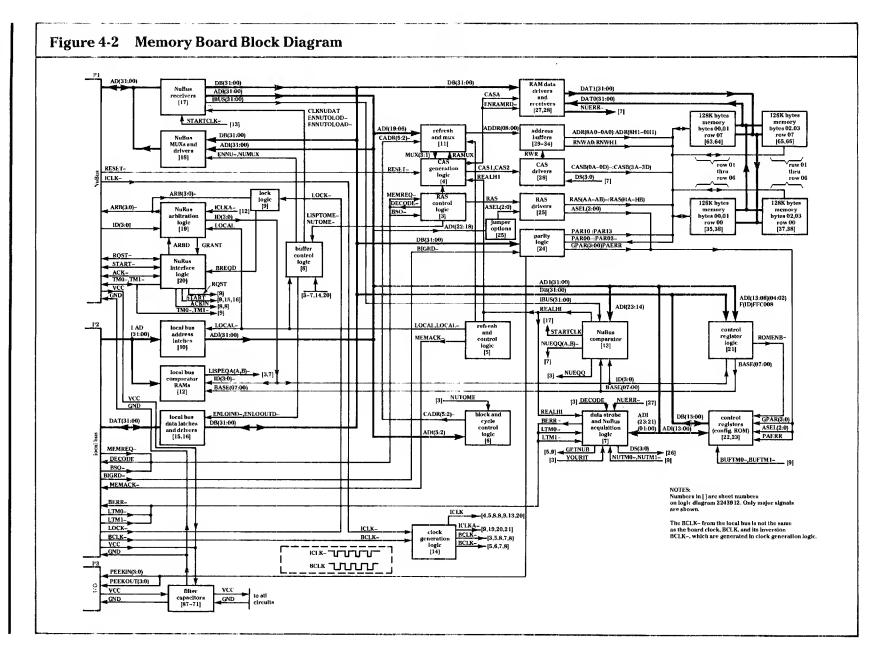

**4.2.2** The control register logic on the memory board contains a physical base register that has a BASE(07:00) code output. The function of the base register is to allow the data memory starting address to be moved to any location in the 4-gigabyte memory space addressed by the full 32-bit address configuration. The eight most significant address bits are supplied by the base register. After power-up or reset, the base register is loaded with >FS, where S is the board slot ID number. The memory control space used by the configuration ROM and the on-board registers is not moved by the base address register.

**NOTE:** In the BASE(07:00) code, (07:00) indicates bits 00 through 07. This method of indicating bits is followed throughout this document and is standard on the block diagram and the memory board logic diagram.

When the system is initialized on power-up, bits 03:00 of the base register are loaded with the ID(3:0)- code from the backplane, and bits 07:04 of the base register are set. This allows the system software to address 256 megabytes of memory data at address >FSXXXXX. After all initialization is complete, the system software can address other 256-megabyte sections of memory by writing the desired address bits into the base register. This allows large memories to be addressed using all of the 32-bit address capacity of the NuBus and local bus.

The base register is loaded by writing data bits DB(07:00) at address >FSFFC008. Control space resides at >FSFFC000 through FSFFFFFF, and control register 00 resides at location >FSFFC000, regardless of the contents of the base register. The full 32-bit address configuration is shown in Figure 4-3.

| Figure 4-4 | NuBus Bit Orga | nization    |        |        |  |  |  |

|------------|----------------|-------------|--------|--------|--|--|--|

|            | bit 31         |             |        |        |  |  |  |

|            |                | 32-bit word |        |        |  |  |  |

|            | halfv          | vord 1      | halfv  | word 0 |  |  |  |

|            | byte 3         | byte 2      | byte 1 | byte 0 |  |  |  |

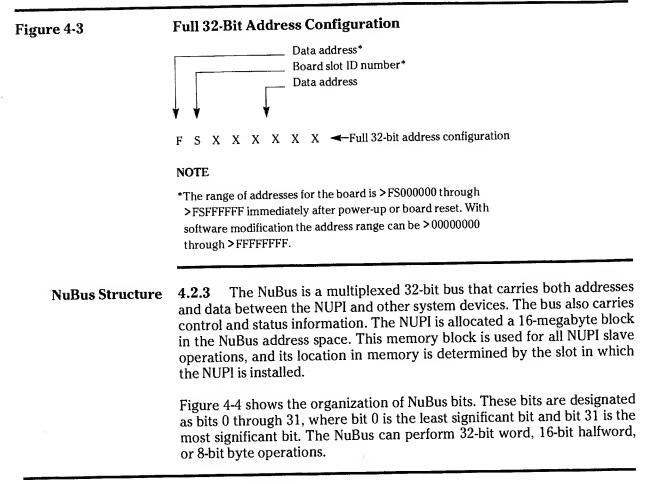

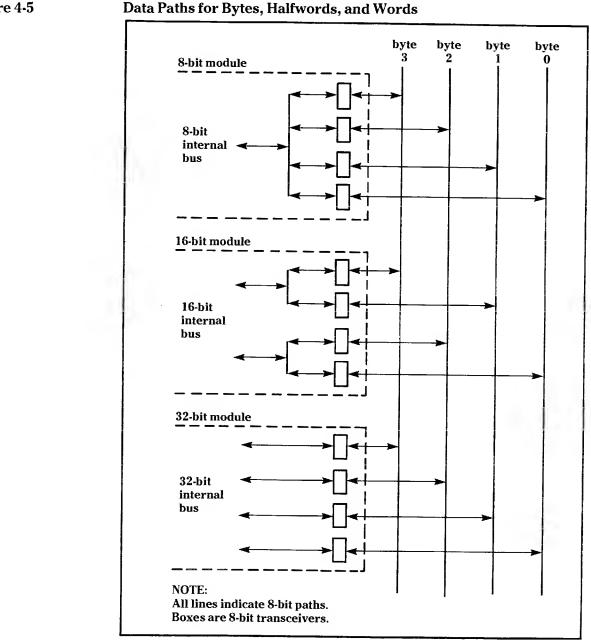

Figure 4-5 shows the data paths for 8-bit bytes, 16-bit halfwords, and 32-bit words over the NuBus. Any given data byte is always carried on the same set of NuBus lines regardless of the transfer mode. The address lines are allocated as follows:

- Byte 0 AD0- through AD7-

- Byte 1 AD8– through AD15–

- Byte 2 AD16– through AD23–

- Byte 3 AD24– through AD31–

This data path approach allows a straightforward connection of either 8-bit, 16-bit, or 32-bit devices.

Figure 4-5

#### Data Transfer **Mode Signals**

Table 4-2 defines the data transfer signals for the NuBus and the 4.2.4 Explorer bus. Signals TM0- and TM1- are part of the NuBus. Signals LTM0- and LTM1- are part of the local bus. The address bits AD0- and AD1- are common to both the NuBus and the local bus. The actual decoding of these signals occurs at the data strobe and NuBus acquisition logic on the block diagram.

The TM0- and TM1- signals have been changed to NUTM0- and NUTM1signals by the lock logic circuits. The data transfer mode signals are decoded to create a DS(3:0) code that is sent to the column address strobe (CAS) drivers. The CAS drivers determine which columns on the memory arrays to address for the type of read or write cycle to be used. The write and read block cycles are supported only when the memory board is a slave to the NuBus.

|               | —— Signals (Lo | nn True) |      |                                |

|---------------|----------------|----------|------|--------------------------------|

| TM1–<br>LTM1- | or TMO-or      |          | AD0- | Type of Read<br>or Write Cycle |

| L             | L              | L        | L    | Write byte 3                   |

| Ĺ             | L              | L        | н    | Write byte 2                   |

| Ĺ             | L              | н        | L    | Write byte 1                   |

| L             | L              | н        | Н    | Write byte 0                   |

| Ĺ             | н              | L        | L    | Write halfword 1               |

| L             | н              | L        | н    | Write block*                   |

| L             | н              | н        | L    | Write halfword 0               |

| L             | н              | н        | н    | Write word                     |

| Н             | L              | L        | L    | Read byte 3                    |

| Н             | L              | L        | Н    | Read byte 2                    |

| Н             | L              | н        | L    | Read byte 1                    |

| н             | L              | н        | Н    | Read byte 0                    |

| н             | Н              | L        | L    | Read halfword 1                |

| Н             | н              | L        | н    | Read block*                    |

| Н             | н              | H.       | L    | Read halfword 0                |

| Н             | Н              | н        | н    | Read word                      |

#### NOTE:

\* The write block and read block cycles are supported only when the memory board is a slave to the NuBus.

#### NuBus Status Code Signals

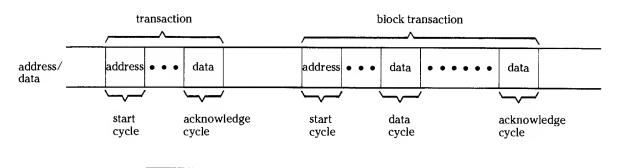

**4.2.5** The NuBus status code signals are shown in Table 4-3. The TMOand TM1- lines provide status information to the current NuBus master during the acknowledge cycle. The memory board can be a NuBus master or slave during single data-cycle transactions. Block transfers are supported only when the memory board is a NuBus slave. The status information is briefly defined in the following items:

- A *NuBus transfer complete* indicates a normal, valid completion of a bus transfer.

- An *error* can occur during a read or write operation. When an error occurs, the transaction terminates in a normal way and the NuBus master assumes the responsibility for handling the error condition.

- A NuBus time-out occurs when an unimplemented address location is requested. This time-out response indicates that the system-defined time-out period has transpired at the same time the NuBus was busy (between start and acknowledge cycles) and no transfer acknowledge has occurred. Bus time-out also occurs when a contender requests the NuBus and does not generate a start cycle. In this case, the NuBus time-out logic generates an idle cycle to reinitiate bus arbitration. Bus time-out responses are generated by the system time-out logic, which is not on the memory board.

- A try again later status code is a response from the addressed slave and indicates that it is not able to respond to a NuBus master's transfer request at the time of the request. The NuBus master will rearbitrate for the NuBus later and try again to get a response from the selected slave.

| ; | NuBus S          | NuBus Status Code Summary |                                                                       |  |  |  |

|---|------------------|---------------------------|-----------------------------------------------------------------------|--|--|--|

|   | Sig<br>TM1-      | nals ——<br>TMO-           | Status Information                                                    |  |  |  |

|   | L<br>L<br>H<br>H | L<br>H<br>L<br>H          | NuBus transfer complete<br>Error<br>NuBus time-out<br>Try again later |  |  |  |

#### Table 4-3

#### NuBus Block Sizes and Starting Addresses

**4.2.6** Table 4-4 lists the NuBus block sizes and starting addresses. Address bits ADI(5:2)- provide the code that indicates the number of words in a block and the block starting address. Address bits ADI(5:2)- are changed to a CADR(5:2)- code at the block and cycle control logic on the block diagram. The CADR(5:2)- code is sent to the refresh and multiplexer logic to become part of the complete word address. If a block transfer is not being implemented, address bits ADI(5:2)- are the same as the CADR(5:2)- code. Only 32-bit word transfers are supported in the block transfer mode.

During block transfers, the memory board is a slave to the NuBus. Block transfers are composed of a start cycle, multiple data cycles to and/or from sequential address locations, and an acknowledge cycle. For each data cycle during a block transfer, the memory board responds to the NuBus using the TMO-, TM1-, and ACK- signals. The intermediate data cycle responses are data cycles where TMO- is asserted and TM1- and ACK- are both unasserted. For intermediate responses, TMO- has the same significance and timing as the ACK- signal during nonblock transfers. The last word transfer in the acknowledge block is indicated when the ACK- signal is asserted.

|        | Addre  | ss Bits |        | Number of      |                        |

|--------|--------|---------|--------|----------------|------------------------|

| ADI05- | AD104- | ADI03-  | ADI02- | Words in Block | Block Starting Address |

| x      | x      | x       | н      | 2              | (AD31-AD03)000         |

| X      | X      | Ĥ       | L      | 4              | (AD31-AD04)0000        |

| x      | Н      | L       | L      | 8              | (AD31-AD05)00000       |

| Н      | L      | L       | L      | 16             | (AD31-AD06)000000      |

#### Table 4-4 NuBus Block Sizes and Starting Addresses

#### NOTE:

AD(31:00)- are NuBus address/data signals. After leaving the NuBus, the AD(31:00)- signals become ADI(31:00) signals on the memory board.

Clock Generation 4

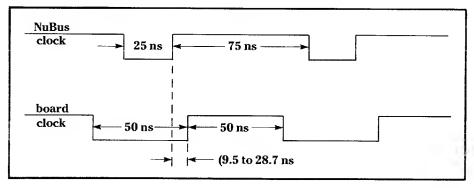

**4.2.7** The bus currently selected by the bus arbitration logic, either the local bus clock (BCLK–) or the NuBus clock (ICLK–) drives the board clock (BCLK) synchronously and in phase. Figure 4-6 and Figure 4-7 illustrate board clock regeneration from the local bus clock and the NuBus clock, respectively.

# Figure 4-6 Board Clock Regeneration From the Local Bus Clock local bus clock board clock clock clock clock clock clock clock clock board clock clock

#### Board Clock Regeneration From the NuBus Clock

**Bus** Arbitration Logic 4.2.8 The bus arbitration selects between NuBus and local bus cycles. The arbitration gives each bus an equal share of the memory board resources. When both buses want access to the board, the one currently selected gets access. After completion of the current cycle, the competing bus is selected.

After initial power-up or a board reset, the NuBus clock is selected to drive the board clock.

Figure 4-7

**NuBus Arbitration 4.2.9** When a NuBus arbitration contest occurs, each board that is a contender drives the ARB(3:0)- lines with its unique ID code. If a board detects a higher ID code than its own on the ARB(3:0)- lines, it removes its ARB(3:0)- code. Then, only the board with the highest ID code is master of the bus.

Arbitration contests last two clock periods by definition. On the second sample edge of the clock after a contest starts, all contenders test their internal GRANT signal. The highest priority contender has its GRANT signal asserted. The winning contender acquires control of the bus and asserts the START- signal on the next assertion edge of the clock. If the bus is in use, the new winner asserts the START- signal on the assertion edge where the current transaction's ACK- signal is asserted. The new winner continues to assert its ID code on the ARB(3:0)- lines during the start cycle of its first transaction to facilitate bus lock detection and bus diagnostics.

**Control Logic 4.2.10** There are four control logic blocks on the memory board block diagram. These are the buffer control logic, refresh control logic, block cycle control logic, and register control logic.

The buffer control logic arbitrates between NuBus to memory requests, local bus to memory requests, local bus to NuBus requests, and refresh cycles. The arbitration between the local bus and the NuBus gives each bus an equal share of the memory board resource. If both buses try to access the memory board at the same time, the bus currently pointed to by the buffer control logic gets access. After completion of the current cycle, the direction changes to allow access from the other bus.

The refresh and control logic, block cycle and control logic, and the register control logic functions are reasonably self-evident from the block diagram.

Local Bus and NuBus Locking

4.2.11 Bus locking is a mechanism used to develop continuous read/write cycles on either the local bus or the NuBus. The local bus is locked to the memory board when the LOCK- signal is asserted. The NuBus is locked when a master continues to request and contend for the bus. Because the master in this case has the highest ID code of the boards present, it wins arbitration contests that follow.

# **Jumper Options** 4.2.12 The memory board is designed for either 64K-bit or 256K-bit memory chips. Table 4-5 shows the jumper organization for 64K-bit and 256K-bit memory chips. The table also shows the jumper for a memory board fully equipped or half equipped with memory chips. These jumpers are hard-wired, zero-ohm resistors installed at the factory. The information given here is to help understand how the memory board can use either size memory chip. For physical locations of the jumpers, check the memory board assembly drawing.

Jumpers AD049 and AK069 are electrically part of the data strobe and NuBus acquisition logic. All the other jumpers are electrically part of the row address strobe (RAS) driver jumper options logic. The word *in* indicates the jumper is installed. The word *out* indicates the jumper is not installed.

#### Table 4.5Jumpers for 64K-Bit and 256K-Bit chips

| Memory Size                                                 |           |           |           | ——— Jur      | npers —   |           |           |           |

|-------------------------------------------------------------|-----------|-----------|-----------|--------------|-----------|-----------|-----------|-----------|

|                                                             | AD049     | AK069     | CC074     | <i>CC079</i> | AK064     | CC064     | BG064     | BG044     |

| 64K-bit chips<br>256K-bit chips<br>Full board<br>Half board | In<br>Out | In<br>Out | In<br>Out | In<br>Out    | Out<br>In | Out<br>In | Out<br>In | Out<br>In |

#### NOTE:

Jumpers are factory-installed, hard-wired, zero-ohm resistors.

To locate the jumpers, physically, look at the board oriented as shown in Figure 1-1. AD, AK, and so on are row designations at the sides of the board. Vertical column positions are numbered horizontally at the top of the board: 03, 07, 11, and so on.

Memory Address

Development